Introduction to High Speed PCB Design

Regardless of whether clock-rates are in the gigahertz range, it is now commonplace to utilize High Speed design principles. High Speed PCB design practices are now essential for producing high signal quality in many of today’s components. For example, DDR3, DDR4 and DDR5 SDRAM. The need for High Speed layout techniques that use constraints has been driven by improvements in product performance, and the pervasive need for device connectivity.

eCADSTAR’s High Speed applications have a consistent user interface. This provides a range of functionality, from design capture to physical layout. The built-in Constraint Browser allows you to manage the complexities of High Speed layout and routing. You can specify constraints in the schematic design and PCB design tools, and in the design rules stacks in Constraint Browser.

The High Speed capabilities of eCADSTAR are listed below.

| Value | Description |

|---|---|

| Impedance Controlled Routing | Both single-ended and differential impedance can be specified to meet the constraints on each board layer. |

| Length, Delay and Skew Based Routing | eCADSTAR allows you to set both length and delay constraints, and can automatically lengthen tracks to meet defined constraints. |

| Topology Control | High-Speed signals require a routing topology that adheres to specified constraints. eCADSTAR allows you to control topologies using a range of default templates. You can also manually create user-defined topologies. By instantly visualizing topologies in this way, you can configure them quickly and reliably. |

| Handling of Differential Signals | Differential signals can be trunk routed using automatic, near end routing that incorporates specified design rules and constraints. |

In this training, you will complete the following tasks.

- Create and configure design items, such as Differential Pairs and buses, which are required for High-Speed design.

- Create custom topologies from a predefined topology list, and apply them to signals in Constraint Browser.

- Create Skew Groups using signals within Constraint Browser, and apply constraints.

- Route to topologies using the tools in eCADSTAR PCB editor.

- Lengthen topologies in order to meet length and skew constraints.

eCADSTAR Applications for High Speed Design

- eCADSTAR PCB Editor: allows you to create instances of High Speed routing.

- Constraint Browser: allows you to define High Speed constraints.

- Topology Template Manager: allows you to define High Speed topology templates.

Note

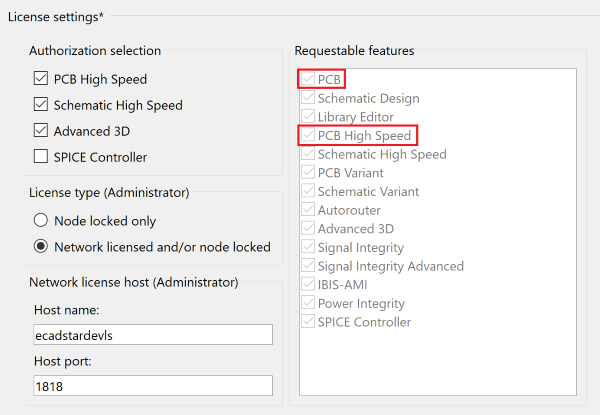

Licenses for PCB and PCB High Speed features are required to follow this training. Check the licensed features as follows.

1. On the eCADSTAR PCB Editor ribbon, click File > Configuration > Product Settings. The Product Settings dialog is displayed.

2. In the Product Settings dialog, select License Settings. The licensed features for eCADSTAR are displayed in the Requestable features box. This is illustrated below.

Figure 1: Licence settings Section

Training Files

The following training files are provided for this course.

- DIY_HS_1_start.pdes: the base design. This is unrouted, and has no topologies or constraints.

- DIY_HS_1_partial_routed.pdes: the base design, which is partially routed with topology templates and is constrained.

- DIY_HS_1_routed.pdes: the base design with topology templates. It is constrained and routed, and some lengthening is applied.