The Net/Bus Mismatch section in the DRC Settings dialog allows you to check the connection status of nets and buses.

| Sub-category | Output Message | Description |

|---|---|---|

| Undefined Net Label | No net label was input. | The syntax of the net label is checked. |

| Undefined Bus Label | No bus label was input. | The syntax of the bus label is checked. |

| Net Label Notation Mismatch | Illegal net label | The syntax of the net label is checked. |

| More than one net label was input for one net. | ||

| Bus Label Notation Mismatch | Error in bus notation. | |

| Connector Notation Mismatch | No net label was input for the connector. | The syntax of the connector's part name is checked. |

|

|

Illegal characters were used in the connector's net label, error in the bus notation. |

|

|

Block/Block Pin Mismatch |

Pin labels were not input for this block. |

Inconsistency is checked for in block and block pin notations. |

|

|

Illegal characters are used for pin labels of the block, or error in duplicate components' notations. |

|

|

|

Duplicate pin labels in one block. |

|

|

|

No block reference was input. |

|

|

|

Illegal characters were used in block reference, or error in duplicate components' notations. |

|

|

|

Blocks with the same reference are included in the same hierarchy. |

|

| Bus/Net Connection Mismatch | No bus label was input for the connected bus. |

Inconsistency is checked for between the bus, and the excluded net.

|

| The label of the connected bus is inconsistent with the net label. | ||

| Single net connection is missing from the bus. | This message is shown if the target net is not connected to the bus. It is also shown if multiple non-target nets are connected to the bus. | |

| Connection Mismatch | The pins on the block do not match the hierarchy connectors. |

Connection mismatch is checked for.

|

| Hierarchy connectors do not match the pins on the block. | ||

| Connectors with different net labels were connected. | ||

| Net label assigned to the connector does not match the one assigned to the connected net. | ||

| Dangling Connector | Dangling connector. | Connectors are checked for that are not connected to anything. |

| Dangling Net | Nets are checked for where there is only a single active device on the net, so the termination of the net ends on a passive device. | The DRC check expects to encounter a component pin that is attached to an active device which is capable of receiving a signal. |

| Bus Bit Count Mismatch | Bit count mismatch between the bus and the connector. | Checks the bit count consistency between the bus name, and the connected connector (sheet connector, power, ground, global connector) . |

| Bit count mismatch between the bus and the block pin. | Checks the bit count consistency between the bus name, and the connected block pinLabel. | |

| Bit count mismatch between the bus and the hierarchy connector. | Checks the bit count consistency between the bus name, and the connected hierarchy port partName. | |

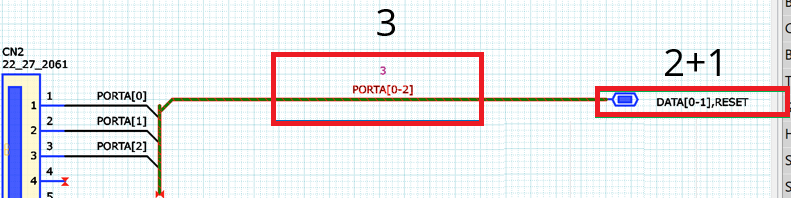

| Bus Bit Order Mismatch | Bit order mismatch between the bus and the connector. | Checks the bit order for the bus name, and the partName of

the connector that it is connected to. This could be a sheet connector,

power, ground or global connector.

Bit order describes the format of the labels

that are displayed in eCADSTAR Schematic Editor

for busses, pins and parts.

The following example shows a bit order mismatch between a bus and the connector.

|

| Bit order mismatch in the hierarchy connection. | Checks the bit order for the bus name of upper hierarchy, the block pin, the hierarchy port partName, and the bus name of lower hierarchy. See Bus Bit Order Mismatch, above for an explanation of bit order. | |

| Same Net Label to Different Nets | Same net Label is used for the separate net/bus objects without sheet connectors. |

The net labels are checked for duplicates.

|

| Unconnected Net to any Part/Gate | Contains a net that is not connected to a part/gate. | Nets are checked for that have no connection to components or gates. |

| Power component with single sub-net | Power supply component that exists independently. | Checks for independent power supply components. |

| Ground component with single sub-net | Ground component that exists independently. | Checks for independent ground components. |

| Duplicated net name connected to both ends of 2-terminal component | Checks 2 pin components with the same net connected on either side. | If nets with the same net name are connected to a two-terminal component, it will be detected as an error. |

| Cross Connection | Defects net cross connections | Creates and error if single net connections create a cross connection. |